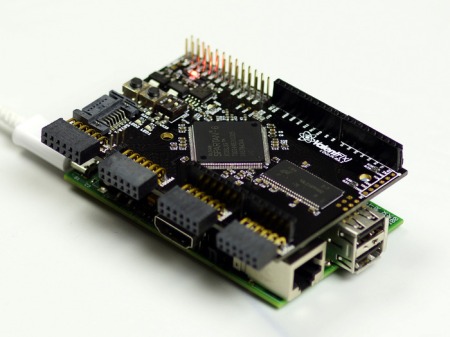

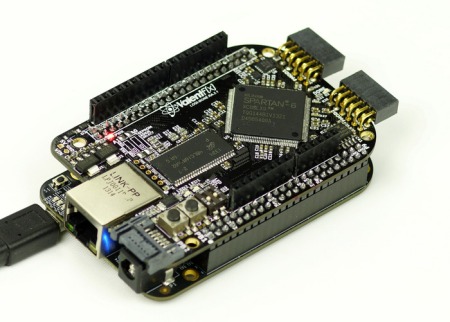

AV-LX9 MicroBoard is a new low cost Spartan-6 LX9 device based development kit from Avnet. XC6SLX9

has 1,430 slices, or 5,720 LUTs, and 32 Block RAM. Rich features, such as 64MB DDR, 128Mb SPI Flash, 10/100 Ethernet PHY, USB-UART port, JTAG, LEDs, DIP switches and expansion ports, make the board an affordable and very useful experimental prototyping tool.

Thanks for Avnet’s Frank for the LX9 MicroBoard, I was lucky to be able to try out the board early. My main goal was to get Petalinux running on this this USB-stick form factor board, with httpd server serving web pages and certain peripherals to demonstrate user defined functionalities. After many weekends’ efforts, I was always couple hundreds of LUTs in short to fit designs of MicroBlaze with MMU into LX9 device, even after removing most peripherals, and enabling Legalizer placement algorithm.

Then Petalogix’s John offered me a Linux BSP, used for hobby purpose. This convinced me the goal was possible, and kept me trying my own SOPC designs.

Finally I got it working before the recent Avnet LX9 MicroBoard SpeedWay Design Workshops. The keys were to remove non-essential MicroBlaze features and not use MDM’s JTAG-based UART thus saves a AXI4-Lite connection. I am sure it can go further to use less resources and/or add more peripherals, but still has a stable Linux running on the board.

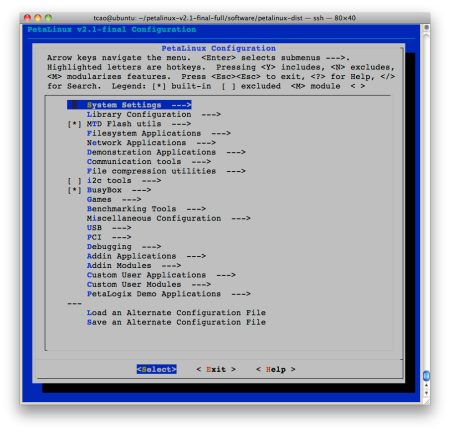

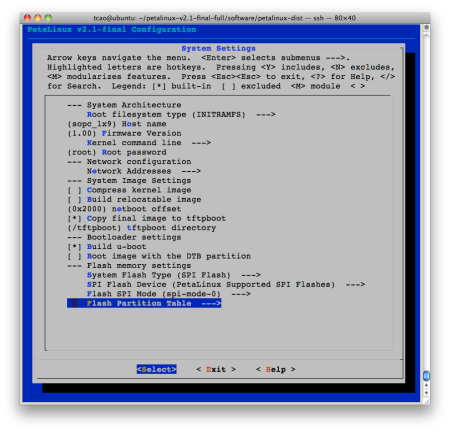

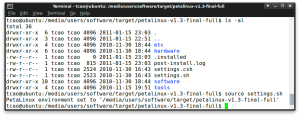

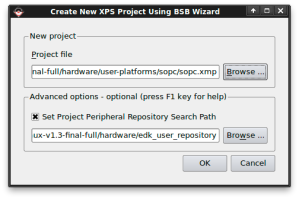

Here’s how the working design was done in details. I am using PetaLinux SDK 2.1 and ISE 13.2 for 32 bit Linux, starting design flow from Project Navigator.

Create a new project based on Avnet LX9 MicroBoard XBD.

Create New ISE Project

Select Embedded Processor for Source Type with New Source Wizard.

Select Source Type

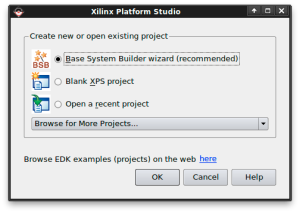

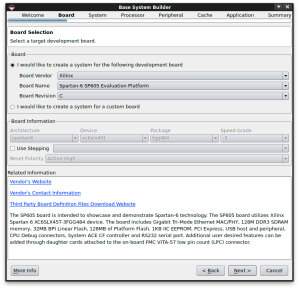

When BSB starts, choose AXI flow.

AXI Flow

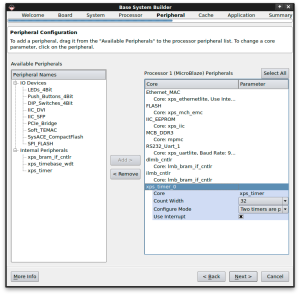

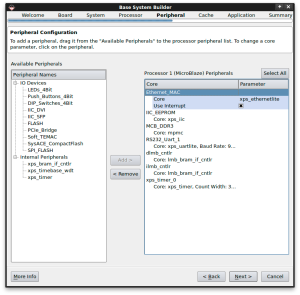

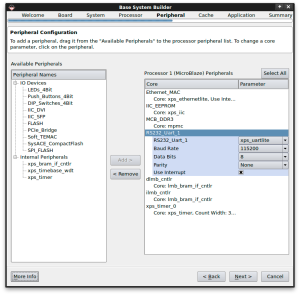

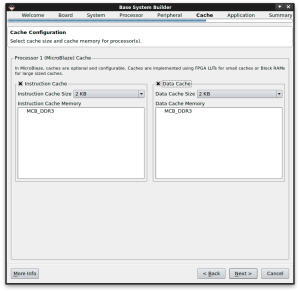

And configure below processor, cache and peripherals.

Processor, Cache and Peripheral Configuration

Once XPS project is created, configure MicroBlaze by double clicking the IP from System Assembly View.

MicroBlaze with MMU Configuration

After select MMU configuration, click Advanced button to fine tune. The following setups can be done by going back and forth to enable then disable certain features. Here’s General configuration.

MicroBlaze General Configuration

Disable all exceptions.

MicroBlaze Exception Configuration

Make sure instruction cache base address is setup properly. This is the location where Linux kernel starts.

MicroBlase Cache Configuration

Here’s MMU setup.

MicroBlaze MMU Configuration

Enable MDM so XMD can be used to debug.

MicroBlase Debug Configuration

No need for Processor Version Registers.

MicroBlase PVR Configuration

Here’s the Interconnection I used.

MicroBlaze Interconnect Configuration

Buses setup is the last MicroBlaze configuration.

MicroBlaze Buses Configuration

Now configure MDM by disabling JTAG UART.

MDM Configuration

Here’s XPS System Assembly View when design is done.

XPS System Assembly View

Return to Project Navigator when XPS is closed. Add constraints by Project > Add Copy of Source.

ISE Add Constraints

Double click Generate Top HDL Source to create HDL instantiation template for the MicroBlaze design.

ISE Generate Top HDL Source

Export hardware design to SDK.

ISE Export Hardware To SDK with Bitstream

If there are errors for placement and routing, try to set environment variable XIL_PAR_ENABLE_LEGALIZER to 1, and rerun PAR.

Here’s my XPS Synthesis Summary (estimated).

XPS Synthesis Summary

Here’s partial ISE Device Utilization Summary.

ISE Device Utilization Summary

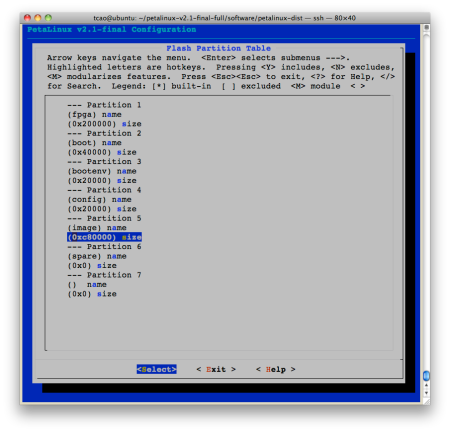

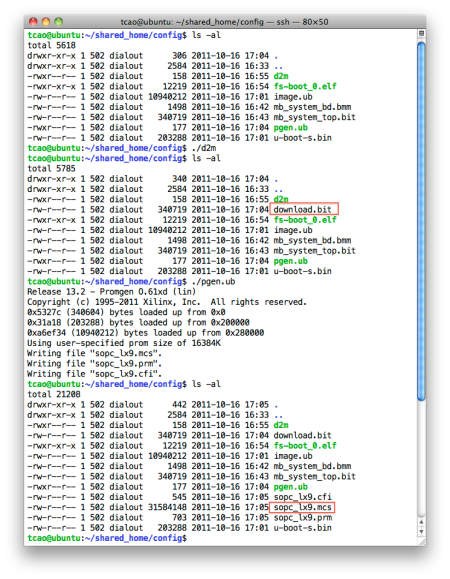

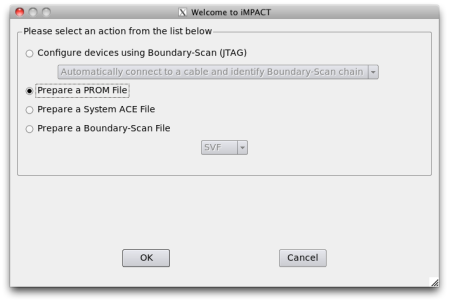

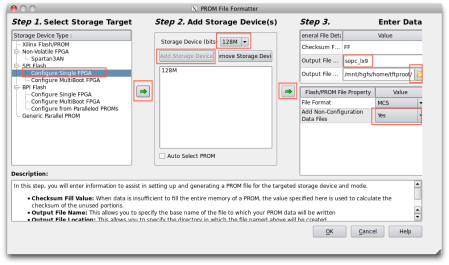

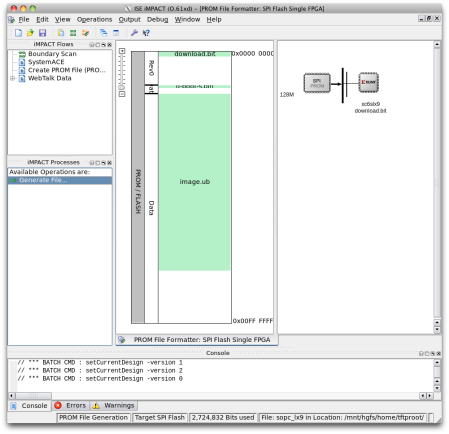

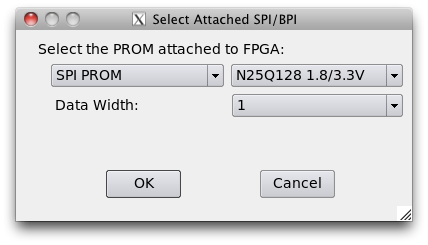

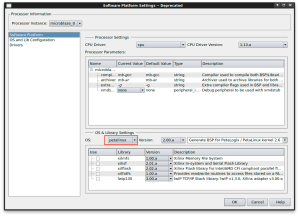

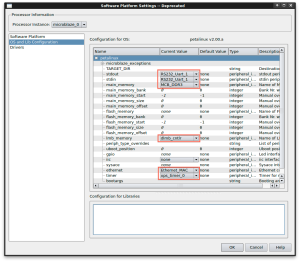

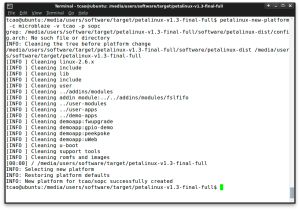

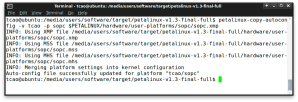

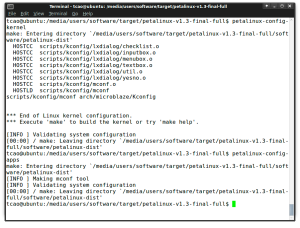

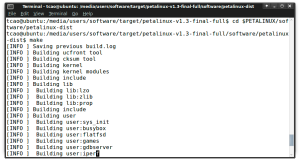

Follow PetaLinux SDK Board Bringup Guide to configure software settings of the hardware project and fs-boot.

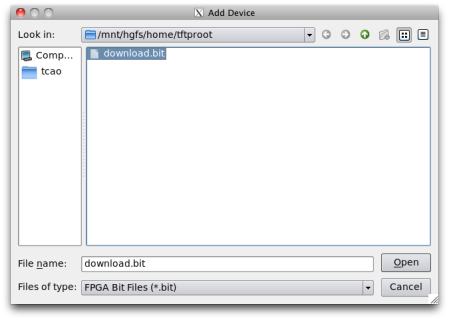

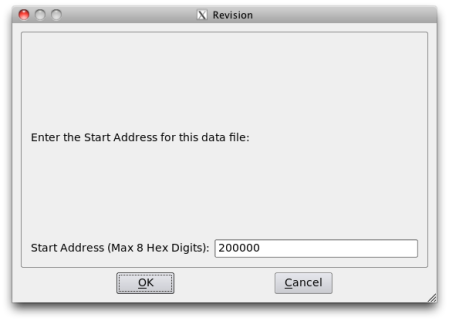

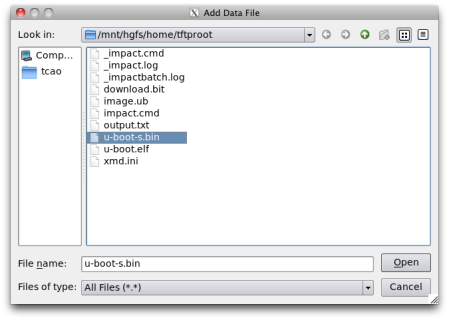

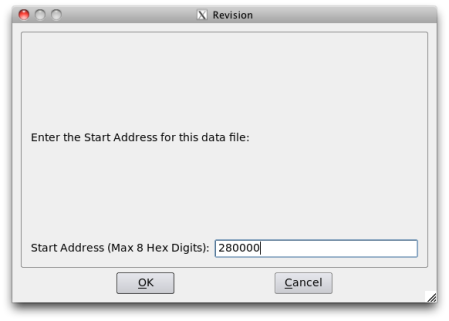

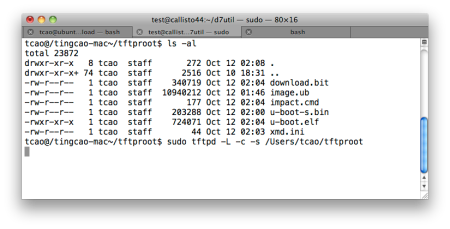

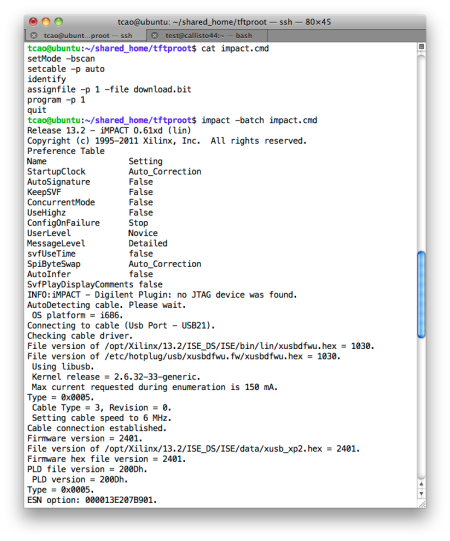

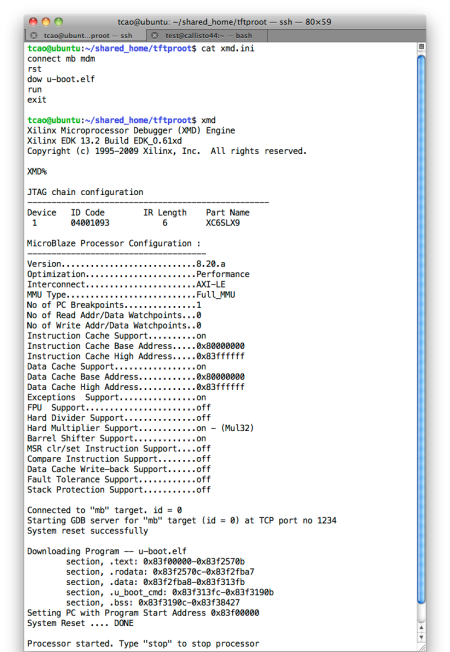

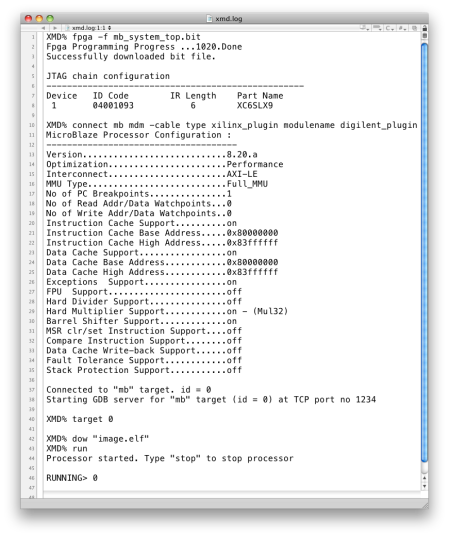

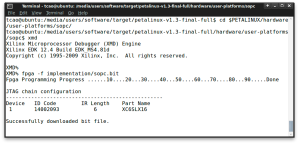

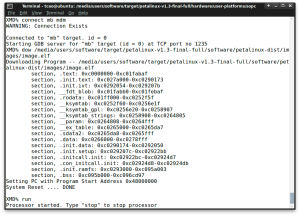

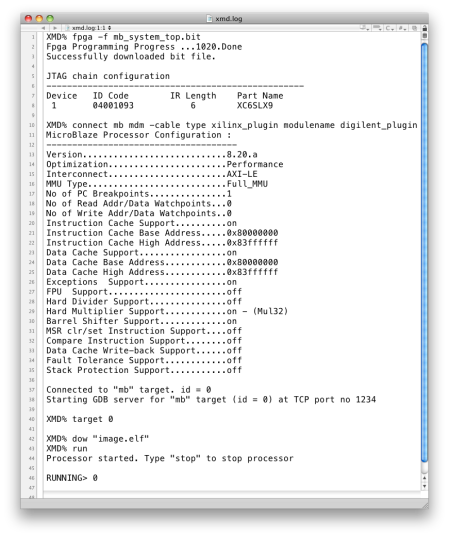

I am using the following XMD commands to configure FPGA and download Linux image.

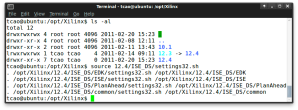

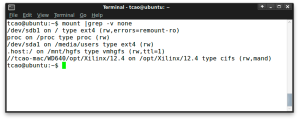

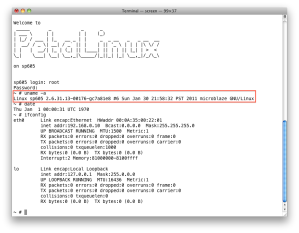

This is the PetaLinux login screen.

This is the PetaLinux login screen.

PetaLinux Login Screen

And PetaLinux Process Status.

PetaLinux Process Status

Another fun experiment is to write code to turn on and off LEDs in certain patterns. 4 bit LED IP’s address is 0x40000000, to turn on all LEDs, you can use:

poke 0x40000000 0x0f

Let me know if you’re interested running my design, I have it here. If you like to try the commercial PetaLinux, please contact Petalogix.