While exploring project ideas for DECA, a new Altera MAX10 FPGA board from Arrow/Terasic (I will cover it in a later series), I’m curious about FPGA graphics capability. I checked it out with a Cyclone V SoCKIT I had since last year.

I found Terasic SoCKIT VIP (Altera Video and Image Processing Suite) reference design from RocketBoards. It does a really good job to demonstrate video features of VIP. I modified the FPGA design to address more on graphics, by removing Logo generator I don’t need, and adding a frame reader of 800×480 pixels and 32 bit per pixel to support graphics, and reusing the first frame reader of 640×480 pixels for graphics too.

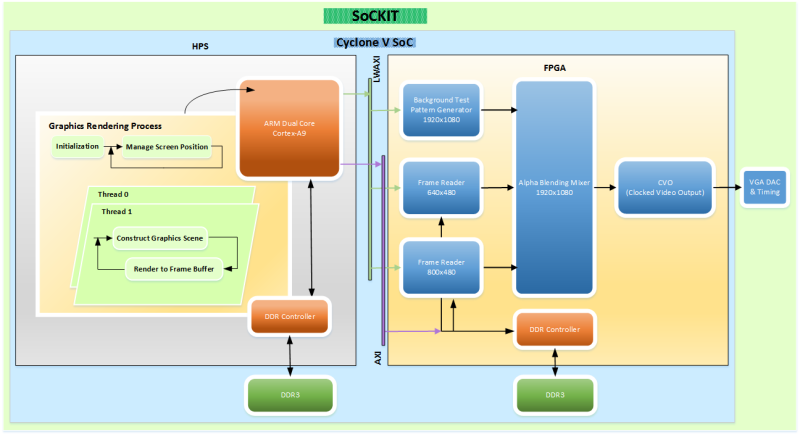

The following picture shows the FPGA hardware setup, basically VIP, and software process for graphics rendering.

The rendering process consists of two threads handing graphics; and each thread corresponds a VIP Frame Reader, as indicated on the right side of FPGA setup of above picture.

- The first 640×480 pixel graphics loops through a sequence of PNG files to show a snowfall. Except for transferring decoded PNG data directly into the frame buffer, it doesn’t do much else. The main parent process also adjusts this graphics’ position such that it bounces around within the screen.

- The second 800×480 pixel graphics renders a Automotive HMI design. The graphics is using XFree86 frame buffer pipeline and proprietary engine.

The following video click shows the process showing the graphics: turn on the SoCKIT board; bring up ethernet so software application can be downloaded to FPAG and debugged via ARM DS-5 Altera Edition; configure the FPGA; and finally run the graphics application.

This exercise lays a solid foundation for my next tackling to get graphics working on Altera MAX 10 DECA board.