AV-LX9 MicroBoard is a new low cost Spartan-6 LX9 device based development kit from Avnet. XC6SLX9

has 1,430 slices, or 5,720 LUTs, and 32 Block RAM. Rich features, such as 64MB DDR, 128Mb SPI Flash, 10/100 Ethernet PHY, USB-UART port, JTAG, LEDs, DIP switches and expansion ports, make the board an affordable and very useful experimental prototyping tool.

Thanks for Avnet’s Frank for the LX9 MicroBoard, I was lucky to be able to try out the board early. My main goal was to get Petalinux running on this this USB-stick form factor board, with httpd server serving web pages and certain peripherals to demonstrate user defined functionalities. After many weekends’ efforts, I was always couple hundreds of LUTs in short to fit designs of MicroBlaze with MMU into LX9 device, even after removing most peripherals, and enabling Legalizer placement algorithm.

Then Petalogix’s John offered me a Linux BSP, used for hobby purpose. This convinced me the goal was possible, and kept me trying my own SOPC designs.

Finally I got it working before the recent Avnet LX9 MicroBoard SpeedWay Design Workshops. The keys were to remove non-essential MicroBlaze features and not use MDM’s JTAG-based UART thus saves a AXI4-Lite connection. I am sure it can go further to use less resources and/or add more peripherals, but still has a stable Linux running on the board.

Here’s how the working design was done in details. I am using PetaLinux SDK 2.1 and ISE 13.2 for 32 bit Linux, starting design flow from Project Navigator.

Create a new project based on Avnet LX9 MicroBoard XBD.

Select Embedded Processor for Source Type with New Source Wizard.

When BSB starts, choose AXI flow.

And configure below processor, cache and peripherals.

Once XPS project is created, configure MicroBlaze by double clicking the IP from System Assembly View.

After select MMU configuration, click Advanced button to fine tune. The following setups can be done by going back and forth to enable then disable certain features. Here’s General configuration.

Disable all exceptions.

Make sure instruction cache base address is setup properly. This is the location where Linux kernel starts.

Here’s MMU setup.

Enable MDM so XMD can be used to debug.

No need for Processor Version Registers.

Here’s the Interconnection I used.

Buses setup is the last MicroBlaze configuration.

Now configure MDM by disabling JTAG UART.

Here’s XPS System Assembly View when design is done.

Return to Project Navigator when XPS is closed. Add constraints by Project > Add Copy of Source.

Double click Generate Top HDL Source to create HDL instantiation template for the MicroBlaze design.

Export hardware design to SDK.

If there are errors for placement and routing, try to set environment variable XIL_PAR_ENABLE_LEGALIZER to 1, and rerun PAR.

Here’s my XPS Synthesis Summary (estimated).

Here’s partial ISE Device Utilization Summary.

Follow PetaLinux SDK Board Bringup Guide to configure software settings of the hardware project and fs-boot.

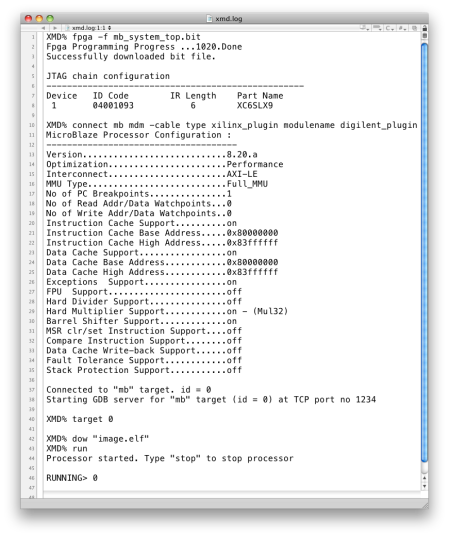

I am using the following XMD commands to configure FPGA and download Linux image.

This is the PetaLinux login screen.

This is the PetaLinux login screen.

And PetaLinux Process Status.

Another fun experiment is to write code to turn on and off LEDs in certain patterns. 4 bit LED IP’s address is 0x40000000, to turn on all LEDs, you can use:

poke 0x40000000 0x0f

Let me know if you’re interested running my design, I have it here. If you like to try the commercial PetaLinux, please contact Petalogix.

September 18, 2011 at 9:28 am |

Hello Mr CAO,

I would like to use microblaze and linux to interface a system using TCP/IP. Specifically, my system needs to give dynamic IP to the device connected to it, I mean it should act as a DHCP server.

Is your design suitable for this, can I directly use your bit file for my lx9 microboard?

You said “If you like to try the commercial PetaLinux, please contact Petalogix.” is the commercial version free? what is the difference between commercial version and the one you used?

I would appriciate if you can help me.

Thanks for your help.

September 18, 2011 at 4:07 pm |

When I did the design (just for LX9 MicroBoard), I used static IP address.

I’m sure you can enable DHCP server, either during kernel config, or add that functionality as a custom app.

I will check that out when I have time.

You’re welcome to use my bit file.

If you want to build your own custom Linux kernel for Spartan-6 device MicroBlaze, you have two options:

1) Use free distribution:

Michal Simek

http://www.monstr.eu/wiki/doku.php?id=start

Xilinx

http://xilinx.wikidot.com/microblaze-linux

2) Use the commercial Petalinux, which is not cheap, but will get you to the market sooner.

This is what I’m using, but will try 1) later.

September 19, 2011 at 1:34 pm |

Hello Mr CAO,

Firstly I wanna thank you for your help. I used your .bit and .elf files and started linux on my microboard. But when I restart my board, I think I need to reload the image. I can convert bit file to mcs file and load it to flash so, FPGA can boot with microblaze. Is there a way that when FPGA boots, microblaze starts with Linux and I dont have to download linux again?

Waiting to hear from you,

Thanks.

September 19, 2011 at 1:45 pm |

Actually that’s what I’m going to do:

1) program SPI flash, so the board is configured when powered on.

2) add more peripherals, like DIP? Hope there is still resource left.

3) add more apps, to drive LEDs? Hope I can time to do it.

So expecting another post or two in coming weeks.

September 19, 2011 at 1:59 pm |

When we program SPI flash, board will be configured with just microblaze not linux, we will have to download linux again. Am I true?

Is not there a way to boot with microblaze and linux together so it is a stand alone module?

September 19, 2011 at 3:07 pm |

No, the board can be configured to boot linux, w/o downloading anything.

September 19, 2011 at 4:19 pm

Can you please direct me about how to do that?

September 20, 2011 at 3:18 pm

Following Xilinx Application Notes are useful:

xapp978 – FPGA Configuration from Flash PROMs on the Spartnan-3E 1600E Board

xapp1146 – Embedded Platform Software and Hardware In-the-Field Upgrade Using Linux

There are some more.

Also if you are a registered user for Avnet’s website (Support Files & Downloads from http://www.em.avnet.com/s6microboard), you can get some LX9 MicroBoard tutorials, one is for SPI flash:

EDK – Creating a MicroBlaze SPI Flash Bootloader (Zip)

Solution: SPI Flash Bootloader (Zip)

September 21, 2011 at 6:38 am

I read many papers including the ones you offered. As I understand I should load the mcs file to flash starting from 0x000000 address and load the image to flash starting from an address you defined while creating the boot loader. Because your bootloader says “No existing image in the flash”.

If I am true, can you send me the address where image should start?

In some documents it says .elf can not be directly loaded, it should be converted to another format(some say .srec, some say .bin, some say .b).

Can you tell me which format your design requires?

September 28, 2011 at 6:27 am

I didn’t design the bit/elf for splash programming, but now I’m still trying to do that.

Also there is a useful discussion about SPI programming. I tried, but didn’t get to the end because I didn’t setup tftp.

http://community.em.avnet.com/t5/Spartan-6-LX9-MicroBoard/Remarks-on-AvtS6LX9MicroBoard-SW302-PetaLinux/td-p/3417

October 13, 2011 at 1:27 am

I had another posting about FPGA/SPI Flash configuration. You can find the download at the end.

Here’s the post link:

October 17, 2011 at 3:13 am |

[…] The FPGA design is done with ISE 13.2 based on AXI/Little Endian MicroBlaze 8.20a. The details were presented here at Run Linux on Avnet Spartan-6 LX9 MicroBoard. […]

October 18, 2011 at 4:40 pm |

I have followed your instructions and generated the hardware design. My axi.4_0_wrapper is almost twice as big as yours (562f/f 375 LUTs). Did you change the configuration of the AXI4 wrapper?

Sven

October 18, 2011 at 9:18 pm |

Hi Sven, I didn’t change AXI configuration, and not sure why your AXI4 wrapper takes more resources.

I believe AXI4 is only used by external memory LPDDR.

I did change how to use AXI4 Lite for peripherals. In my design, I removed MDM’s AXI4 Lite connection (JTAG/UART). That’s one of the two keys to fit the design into LX9 device.

Here’s my MHS if you’re interested.

By the way, I read all (almost, 🙂 ) of your blogs, way back several years ago. I’m still enjoying to read them. Great work indeed.

Ting

October 20, 2011 at 9:54 am |

Thanks for sending me the mhs file. I was using two different clocks (66MHz and 100MHz) in my system which added a lot of logic.

Sven

October 18, 2011 at 6:22 pm |

Any change to not use petalinux but the following : http://xilinx.wikidot.com/ ???

October 18, 2011 at 6:44 pm |

It is for sure possible. I will try it by using Xilinx’ distribution, probably starting sometime next month

November 4, 2011 at 4:59 pm

I can’t wait for your guide for thisone!

November 4, 2011 at 5:54 pm

I didn’t forget, but I’m sorry I will not have time this month. It will be my first thing (of fpga blog) to do to run Xilinx distribution Linux.

October 20, 2011 at 2:20 pm |

Good article. Its realy nice. More information help me.

October 24, 2011 at 11:24 pm |

nice!

February 26, 2012 at 6:46 pm |

Hi!

I’m trying to make this work without Petalinux and I’m facing a few problems. I think that I’m having some kind of trouble configuring the Linux kernel. Could you post your .config file along the sources of the XPS project? That’d be great!

Thank you!

February 27, 2012 at 12:53 am |

I will get back to you, hopefully soon, once I get the files ready.

Thanks for your interest.

Here’s the .config, I changed it to mb_kernel.config

http://tingcao.s3.amazonaws.com/avnet_lx9_petalinux/mb_kernel.config

Here’s the complete EDK project (note I used ISE to create/manage EDK):

http://tingcao.s3.amazonaws.com/avnet_lx9_petalinux/mb_system.rar

Hope it helps. Please let me know when you get Linux built for MicroBlaze.

I will start working on this soon.

February 28, 2012 at 4:39 pm

Thanks a lot. I will try to use buildroot to create the filesystem and will reach back when I got it. Maybe I’ll even write a short tutorial.

Regards

February 28, 2012 at 1:23 pm |

Hi Mr. CAO,

Clearly i wanna ask you a pretty question? Please can you provide me your custom petalinux vhdl and c codes for educational using? Thanks in advance.

Best regards.

February 28, 2012 at 2:38 pm |

Please check my other comment submitted on 02/27/2012.

The link to the complete EDK project was listed, plus Linux kernel config data.

February 29, 2012 at 10:07 am

Hi Mr. CAO,

Isn’t there any C code about the project application on your link as you mentioned http://tingcao.s3.amazonaws.com/avnet_lx9_petalinux/mb_system.rar? Am I right? Is there any necessity to C codes for upgrade from your petalinux project to my custom project?

I thank you many for your kindly regards.

March 1, 2012 at 2:03 am

You may need some C code in EDK project for driver support of custom IPs, and for bootloader.

But I’m not sure about the copy right issue of FS-Boot used in PetaLinux/MicroBlaze.

March 1, 2012 at 6:57 am |

Hi Mr. CAO,

I started to develop my project and i will feed you about my experiences back. But from now on there is a different problem from C codes issue. Daily problem is; i set environment variable XIL_PAR_ENABLE_LEGALIZER to 1 but anything changes about 3 ERRORS:

ERROR:Place:543 – This design does not fit into the number of slices available in this device due to the complexity of

the design and/or constraints.

ERROR:Place:120 – There were not enough sites to place all selected components.

Total REAL time to Placer completion: 3 hrs 42 mins 59 secs

Total CPU time to Placer completion: 3 hrs 42 mins 48 secs

ERROR:Pack:1654 – The timing-driven placement phase encountered an error.

Is there any knowledge regarding this issue?

Thank you again very much.

March 1, 2012 at 7:07 am |

And i forgot and also my PC uses Windows XP Pro service pack 3. My design suite is ISE 13.2. I try to configure and program my board using iMPACT with the on-board USB-JTAG circuitry.

March 1, 2012 at 4:08 pm |

I would suggest review your design, to drop any IPs not actually needed. Use only one clock source, check Sven Andersson’s comment on 2011/10/20.

Make sure XIL_PAR_ENABLE_LEGALIZER kicks in. If you set it up from a console, start EDK from that same console.

March 4, 2012 at 12:07 pm

Hi Mr. CAO,

I solve the mapping anp placement prolem. But still i have a problem too. When I do “Export hardware design to SDK with bitstream” and after this i did “Program FPGA” on SDK v13.2 I have my_project.bit files 333 KB and microblaze_0.elf 1KB. I am sure i couldn’t create the right download.bit file. Because these files are dummy files. What will be the problem?

Thank you very much indeed.

March 4, 2012 at 12:12 pm |

And also i have too many warnings on my generation bit file. ISE v13.2 Design Summary says that “No errors and 284 warnings” Is this can be the problem? My computer’s Operating System is Windows XP Pro 2002 with Service Pack 3.

March 5, 2012 at 4:06 pm |

I had tons of warnings too, but it turned to be fine.

March 5, 2012 at 8:41 pm |

With your experience, what am i doing wrong?

March 5, 2012 at 8:45 pm |

Could you please explain with snapshots the musts of creating bit file? Because your sopc_lx9.mcs file is running and its capacity is 30 MByte? But mine is 333 KByte?

March 5, 2012 at 11:24 pm

The actual size is about 1/3 of that of mcs (in ascii encoding).

I have bootloader, Linux kernel and Linux apps built in, that’s why it is about 11M.

March 6, 2012 at 9:53 pm

Hi Mr. CAO,

Can the problem ocuured because of my computer’s operating system Windows XP? At your petalinux project given as .mcs file write “Linux version 2.6.37.4-00532-gb3a5c37 (tcao@ubuntu) (gcc version 4.1.2) #8 Tue Oct 11 00:46:35 MDT 2011”.

Thank you.

March 6, 2012 at 10:08 pm

On which OS (XP, Linux, etc) you run the design tool (ISE/EDK) does no matter. Make sure you include the bit stream, and you app (such as Linux), etc.

March 25, 2013 at 9:13 pm |

Mr. Cao,

Are the pmod connectors wired up on your LX9 Petalinux build?

If so, how?

Thank You,

Tom

March 25, 2013 at 9:40 pm |

Hi Tom, I didn’t use pmod peripherals in my Petalinux build.

I have a camera board which takes 2 pmod connectors, will try it once I get a chance. Since the space is tight on LX9, I probably will do a camera pmod design, and with Xilinx kernel but not with Linux support.

November 18, 2013 at 7:06 am |

Reblogged this on EmbeddedInn.

December 27, 2013 at 1:44 pm |

Hi Cao,

I know that you posted this blog a long time ago but i will be very grateful if you could try to help me.

I’m using ISE 13.2 on windows XP and BXD 13.2 for Avnet LX9 microboard. I followed all yours steps until the Synthesis. I removed MDM’s AXI4 Lite connection (JTAG/UART). I am using only 66 MHz clock but I don’t know why my number of Slice LUTs is at 102% when in your design is amazingly at 84%.

I check your MHS file and i find a little differences I tried too to do the synthesis with your file and I had the same result. Any suggestion?

I couldn’t find XIL_PAR_ENABLE_LEGALIZER variable, in what file is placed? What you means with rerun PAR?

Congratulations for this blog and thank you very much for share your knowledge. Thanks in advance and best regards.

MagicPhoton

January 8, 2014 at 11:44 am |

Hi MagicPhoton,

I noticed the same thing when I moved from ISE 13.1 to ISE 13.2.

I think the reason is that Xilinx has updated some of its IP blocks which made the larger. I never manage to fit the design into the FPGA anymore.

Sven

February 12, 2014 at 1:52 am |

Hello,

I am getting errors when setting the cache addresses like yours…these addresses seem to cover more than 8KB from 0x80000000 to 0x83ffffff?

ERROR:EDK:3900 – issued from TCL procedure “check_cache” line 44

microblaze_0 (microblaze) – Cacheable segment size defined by C_DCACHE_BASEADDR = 0x08000000 and C_DCACHE_HIGHADDR = 0x83FFFFFF must be a power-of-two.

ERROR:EDK:3900 – issued from TCL procedure “check_cache” line 44

microblaze_0 (microblaze) – Cacheable segment size defined by C_DCACHE_BASEADDR = 0x08000000 and C_DCACHE_HIGHADDR = 0x83FFFFFF must be a power-of-two.

ERROR:EDK:3900 – issued from TCL procedure “check_cache” line 44

microblaze_0 (microblaze) – Cacheable segment size defined by C_DCACHE_BASEADDR = 0x08000000 and C_DCACHE_HIGHADDR = 0x83FFFFFF must be a power-of-two.

January 2, 2016 at 4:50 am |

I have deployed petalinux on microboard , now want to test did my user application work on Linux full flesh , which tool-chain i can use to compile my application c code to run on this petalinux ?

I have tried crosstool-ng.org

microblaze-xilinx-linux-gnu-

microblazeel-xilinx-linux-gnu-

microblaze-xilinx-elf

if any other tool-chain plz give me link.

January 2, 2016 at 5:35 am |

The only option is microblaze-xilinx-linux-gnu (big endian and linux).